# Die Logik hinter Null und Eins

# Experimentiersystem für digitale Schaltungen Teil 2

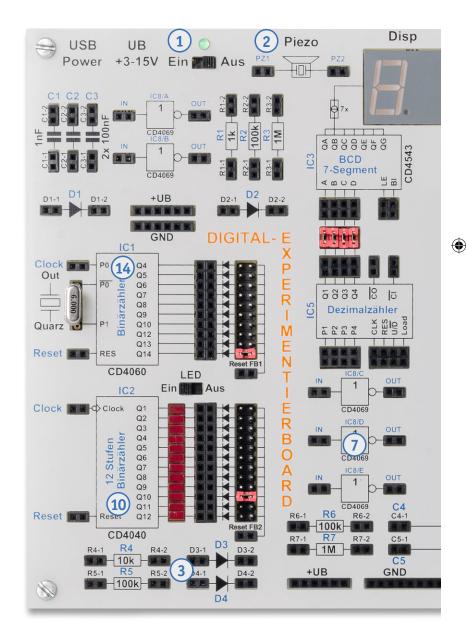

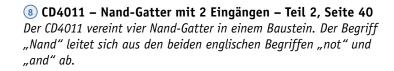

Wir gehen täglich mit Digitaltechnik um, ohne es bewusst zu registrieren. Selbst in der heutigen Zeit, in der wir hauptsächlich mit Mikroprozessoren arbeiten und das Programmieren quasi schon im Schulalter erlernen, ist es unabdingbar, die Grundlagen zu kennen. Schließlich sind einfache Schaltungen auch außerhalb der komplexen Mikroprozessoren nach wie vor eine wichtige Peripherie, deren Funktionen man kennen sollte. Genau diesem Zweck, dem Kennenlernen von Funktionen digitaler Schaltungen, ist das Digital-Experimentierboard DEB100 gewidmet. Es macht den Aufbau, Test und Experimente mit digitalen Schaltungen einfach. Ein perfektes Werkzeug für den privaten Laboreinsatz und in der Ausbildung!

# 1 Spannungsversorgung - in Teil 1

Das DEB100 Experimentierboard kann mit einer Spannung zwischen 3 V und 15 V versorgt werden, dies sind Spannungsgrenzen, die für CMOS-Logikbausteine zugelassen sind.

# 2 Piezo-Signalgeber - in Teil 1

Der Piezo-Signalgeber ist ein Soundgenerator mit einer bestimmten Resonanzfrequenz. Er dient als akustischer Signalgeber für universelle Aufgaben.

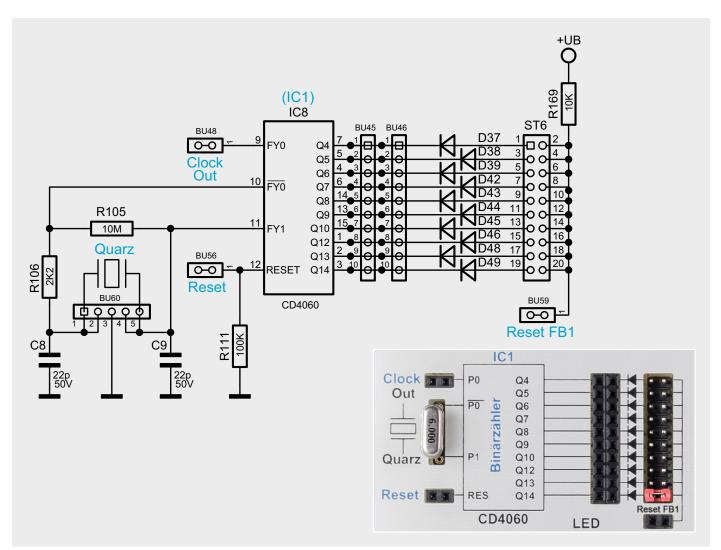

# (4) CD4060 – 14-stufiger Binärzähler mit Oszillator – Teil 2, Seite 49

Der CD4060 ist ein Binärzähler mit 14 Stufen und einem integrierten Oszillator. Dieser Zähler wird gerne als Basisgenerator verwendet, da er einen Oszillator integriert hat. In unserer Schaltung wird standardmäßig ein Quarz mit einer Frequenz von 4,194304 MHz verwendet.

## (10) CD4040 – 12-stufiger Binärzähler – Teil 2, Seite 42

Der CD4040 ist im Prinzip ähnlich aufgebaut wie der CD4060 (s. Nr. 14). Der Unterschied besteht darin, dass es keinen internen Oszillator gibt und der Zähler nur 12-stufig ist. Ein Vorteil ist aber, dass alle Zählerstufen herausgeführt sind.

### 7 CD4069 - Inverter - in Teil 1

Der CD4069 vereint sechs Inverter in einem Baustein. Die Funktion ist schnell erklärt: Ein High-Pegel am Eingang ergibt einen Low-Pegel am Ausgang und umgekehrt.

### 3 Diskrete Bauteile und Bedienelemente – in Teil 1

Für allgemeine Anwendungen befinden sich auf der Platine einige analoge diskrete Bauteile wie Widerstände, Kondensatoren und Dioden. Diese werden für einfache Zeitkonstanten usw. benötigt.

Auf dieser Doppelseite geben wir einen Überblick über die im Bausatz vorhandenen Komponenten. Zu den jeweiligen Baugruppen finden Sie einen Hinweis, ob wir diese in dieser aktuellen Ausgabe ausführlich vorstellen oder bereits in Teil 1 des Beitrags zu dem Bausatz im ELVjournal 4/2019 vorgestellt haben. Teilweise sind Baugruppen auf dem Board mehrfach vorhanden – wir weisen dann beispielhaft auf eine vorhandene Einheit hin.

$\bigoplus$

Bausatzbeschreibung und Montagevideo #10262 Webcode im ELV Shop eingeben oder QR-Code scannen

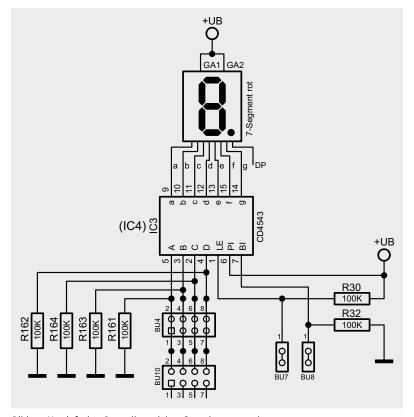

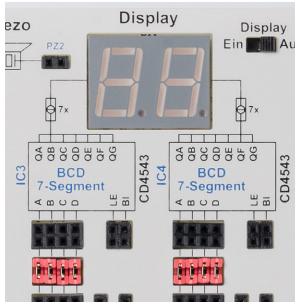

# (3) CD4543 – BCD zu 7-Segment-Decoder (mit Speicher) – Teil 2, Seite 47

Dieser Decoder wandelt einen BCD-Code in eine 7-Segment-Ausgabe für LED- oder LC-Anzeigen um, zudem besitzt dieser Baustein noch einen Eingangsspeicher. In der Regel wird dieser Baustein für LED-7-Segmentanzeigen verwendet.

# 6 Statusanzeige – in Teil 1

Um einen besseren Überblick zu gewährleisten, an welcher Stelle in der Schaltung welcher Logikzustand herrscht, sind an vielen markanten Stellen, z. B. Ausgängen von Zählerstufen, Status-LEDs installiert.

## 9 CD4013 D-Flip-Flop – Teil 2, Seite 41

Der CD4013 vereint zwei D-Flip-Flops in einem Gehäuse. Dieses Flip-Flop kann auf zwei unterschiedliche Arten betrieben werden.

## (1) CD4017 – Dezimalzähler mit 10 Ausgängen – Teil 2. Seite 44

Der CD4017 ist ein synchroner Dezimalzähler mit zehn Ausgängen. Im Gegensatz zu einem Binärzähler ist immer nur einer der zehn Ausgänge aktiv, also ein 1-aus-10-Decoder.

# 5 Logikpegel (4fach) – in Teil 1

Um Logikpegel, also die logischen Zustände in der Schaltung, einfach erkennen zu können, gibt es vier unabhängige Pegeldetektoren, die mittels LEDs den Zustand High oder Low anzeigen.

# 4 Open-Collector-Ausgang – in Teil 1

Für externe Schaltaufgaben steht ein sogenannter Open-Collector-Ausgang zur Verfügung. Hiermit können z. B. kleine Relais geschaltet werden.

# 12 CD4510 – Dezimalzähler (aufwärts/abwärts) – Teil 2, Seite 46

Dieser Dezimalzähler ist sowohl als Aufwärts- als auch als Abwärtszähler konfigurierbar. Zudem ist der Zähler kaskadierbar und der Zählerstand kann geladen werden.

ELVjournal 5/2019

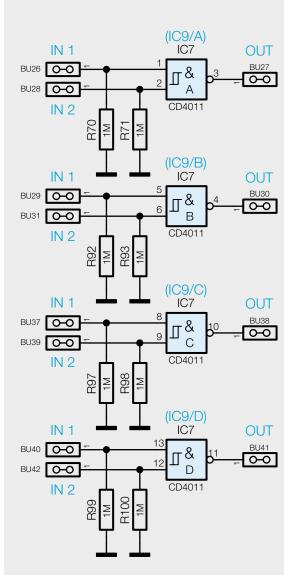

Bild 9: Die vier Gatter des CD4011

www.elvjournal.de ...at ...ch

# ® CD4011 – Nand-Gatter mit 2 Eingängen

Bezeichnung: CD4011, HEF4011 Typ: CMOS Nand-Gatter

mit Eingängen

Betriebsspannung: 3-15 V

Verzögerungszeit: 60 ns @ UB=10 V Ausgangsstrom: 6 mA (typ.)/Gatter

#### Funktion

Der CD4011 vereint vier Nand-Gatter in einem Baustein. Der Begriff "Nand" leitet sich aus den beiden englischen Begriffen "not" und "and" ab. Auf Deutsch würde man sagen, es ist ein "Nichtund". Im Prinzip ist ein Nand- ein And-Gatter (Und-Gatter) mit nachgeschaltetem Inverter. Die Funktion lässt sich am einfachsten in der hier nochmals aufgeführten Wahrheitstabelle erkennen (Bild 11). Der Ausgang "Out" geht nur dann auf Low, wenn beide Eingänge gleichzeitig auf High sind. In Bild 10 ist ein einzelnes Gatter mit Platinenaufdruck zu sehen.

Bild 9 zeigt das Schaltbild des CD4011 so, wie es in unserer Schaltung verwendet wird. In einem Baustein stehen vier Gatter mit je zwei Eingängen zur Verfügung. Die Eingänge sind jeweils mit einem Widerstand nach Masse geschaltet. So wird verhindert, dass nicht benutzte Gatter und Eingänge "floaten" und schwingen. Dies ist eine Grundregel der Digitaltechnik: Eingänge immer definiert abschließen und nie offen lassen!

Bild 10: Nand-Gatter mit dem zugehörigen Platinenaufdruck

| IN1 | IN2 | OUT |

|-----|-----|-----|

| L   | L   | Ι   |

| Н   | L   | Н   |

| L   | Н   | Н   |

| Н   | Н   | L   |

H = High-Pegel L = Low-Pegel

Bild 11: Wahrheitstabelle für ein Nand

# 3x ELVjournal testen für nur € 9,95\*

\*Sie erhalten ab dem nächsterreichbaren Erscheinungsdatum drei aufeinanderfolgende Ausgaben des ELVjournals zum Gesamtpreis von € 9,95. Das ELVjournal erscheint alle 2 Monate, 6-mal im Jahr. Sofern Sie nicht kündigen, verlängert sich der Bezug automatisch zu einem Jahresbezugspreis von € 34,95. Eine Kündigung ist jederzeit möglich. Alle hier genannten Preise gelten nur für Kunden aus Deutschland mit deutscher Lieferanschrift. Weitere Infos zu unseren Abonnements finden Sie auf Seite 113 und unter www.elvjournal.de – www.elvjournal.at – www.elvjournal.ch

29.08.19 14:15

**(**

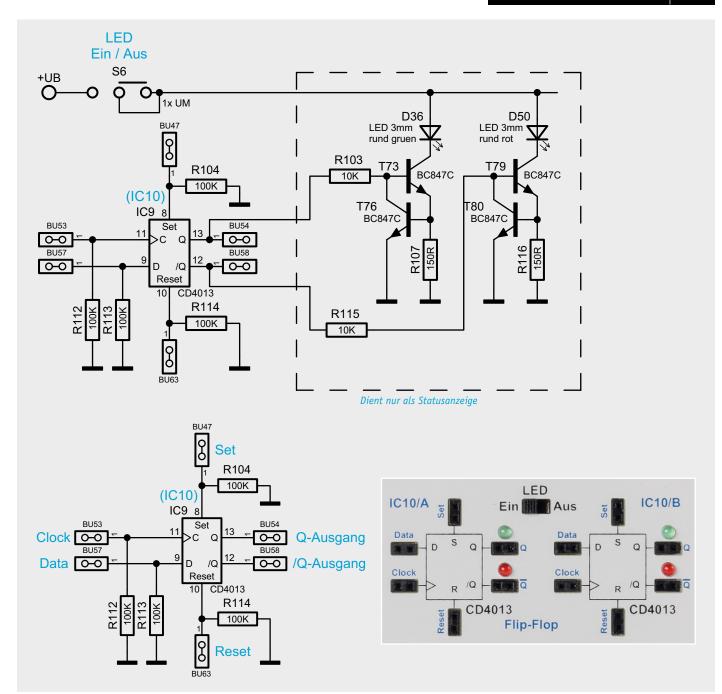

Bild 14: Die Schaltung des CD4013 (oben mit Statusanzeige)

# O CD4O13 D-Flip-Flop

Bezeichnung: CD4013, HEF4013

Typ: CMOS D-Flop-Flop (2 Stück in einem Gehäuse)

Betriebsspannung: 3-15 V

Taktfrequenz: 3,5 MHz @ UB=5 V

10 MHz @ UB=10 V

Stromaufnahme: 0,4–1,5 mA ohne Last

### **Funktion**

lacktriangle

Der CD4013 vereint zwei D-Flip-Flops in einem Gehäuse.

In Bild 14 ist die Schaltung (1/2) des CD4013 (oben mit Statusanzeige, unten vereinfacht ohne Statusanzeige) zu sehen. Dieses Flip-Flop kann auf zwei unterschiedliche Arten betrieben werden. Im getakteten Modus (Bild 15) werden die Eingänge Clock (Takt) und der Dateneingang genutzt. Der Set- und der Reseteingang müssen in dieser Betriebsart auf Masse (Low-Pegel) liegen. Bei jedem Low-High-Wechsel am Clockeingang wird der momentane Pegel am D-Eingang auf den Q-Ausgang übertragen und gespeichert.

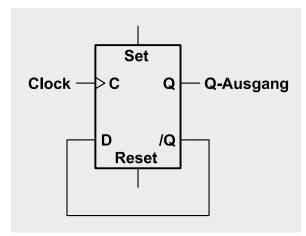

Bild 15: So wird aus einem D-Flip-Flop ein T-Flip-Flop.

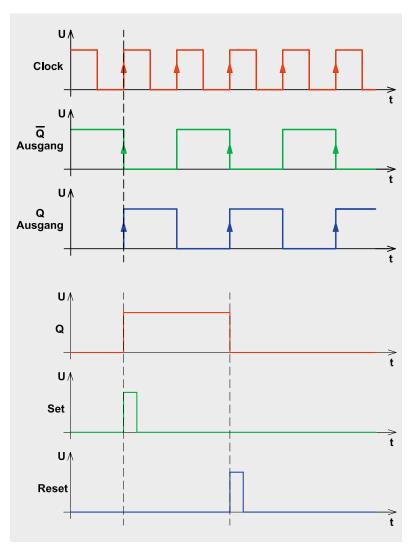

Da es sich um eine Flip-Flop-Schaltung handelt, verhält sich der /Q-Ausgang immer entgegengesetzt zum Q-Ausgang. Liegt während des Low-High-Signals (positive Flanke) ein High am D-Eingang, wird auch der Ausgang Q High führen. Verbindet man den /Q-Ausgang mit dem D-Eingang, erhält man ein T-Flip-Flop, das bei jedem Taktsignal an Clock seinen Ausgangszustand ändert. Im oberen Teil von Bild 16 sind hierfür die Signalverläufe dargestellt.

Die zweite Betriebsart arbeitet mit den Eingängen "Set" und "Reset". Ein High am Eingang "Set" setzt das Flip-Flop (Q = H und /Q = L). Mit einem High am Resetanschluss wird das Flip-Flop zurückgesetzt. Auch hierfür ist im unteren Teil von Bild 16 ein Signaldiagramm dargestellt. Es können aber auch beide Betriebsarten miteinander kombiniert werden.

In der Wahrheitstabelle (Bild 17) sind alle möglichen Pegelzustände an den Eingängen und deren Auswirkung dargestellt.

Wie in Bild 14 zu sehen, sind die Ausgänge mit einer spannungsunabhängigen Statusanzeige versehen. Diese Statusanzeige ist für Eigen- bzw. Nachbauten nicht notwendig. Im unteren Teil von Bild 14 ist die vereinfachte "normale" Beschaltung des CD4013 dargestellt. Mit dem Schalter S6 kann die LED-Statusanzeige deaktiviert werden, falls diese nicht erwünscht ist.

Bild 16: Diagramme für die beiden Betriebsarten des CD4013

| Clock | D (Data) | Set | Reset | Q-Ausgang | /Q-Ausgang | Funktion                            |  |

|-------|----------|-----|-------|-----------|------------|-------------------------------------|--|

|       | Н        | L   | L     | Н         | L          | Daten (H) an "D" werden gespeichert |  |

|       | L        | L   | L     | L         | Н          | Daten (L) an "D" werden gespeichert |  |

| Х     | Х        | Н   | L     | Н         | L          | Flip-Flop wird gesetzt              |  |

| Х     | Х        | L   | Н     | L         | Н          | Flip-Flop wird zurückgesetzt        |  |

H = High-Pegel

L = Low-Pegel

X = Zustand beliebig

Bild 17: Die Wahrheitstabelle für CD4013

# © CD4040 – 12-stufiger Binärzähler

Bezeichnung: CD4040, HEF4040 Typ: CMOS Binärzähler

Betriebsspannung: 3-15 V Frequenz: 2 MHz @ 5 V 12 MHz @ 10 V

Stromaufnahme: 0,04 µA inaktiv 3 mA aktiv

### Funktion

$^{\scriptsize{\scriptsize{\scriptsize{\scriptsize{\scriptsize{\scriptsize{\scriptsize{\scriptsize{\scriptsize{\scriptsize{}}}}}}}}}}}$

Der CD4040 ist im Prinzip ähnlich aufgebaut wie der im folgenden Abschnitt beschriebene CD4060. Der Unterschied besteht darin, dass es keinen internen Oszillator gibt und der Zähler nur 12-stufig ist. Ein Vorteil ist aber, dass alle Zählerstufen durchgängig von Q1 bis Q12 herausgeführt sind.

www.elvjournal.de ...at ...ch

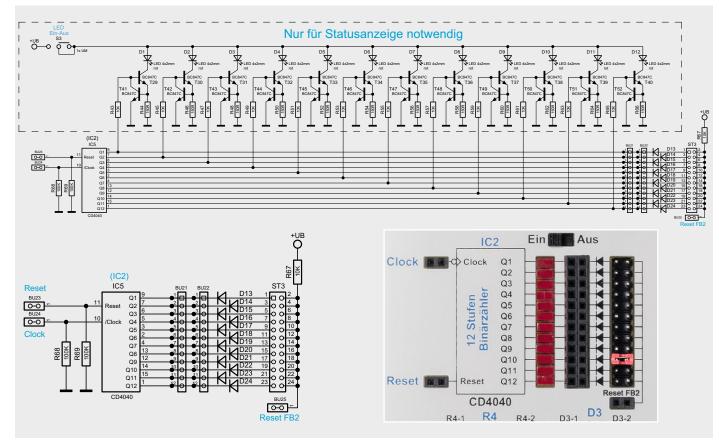

In Bild 21 sind das Schaltbild des CD4040 in unserer Schaltung mit Peripherie und der zugehörige Platinenaufdruck dargestellt. Im oberen Teil ist das komplette Schaltbild mit den Status-LEDs zu sehen. Für das Verständnis und auch zum Nachbau in eigenen Schaltungen sind die Status-LEDs nicht relevant und dienen nur zur Anzeige der Logikpegel an den Ausgängen.

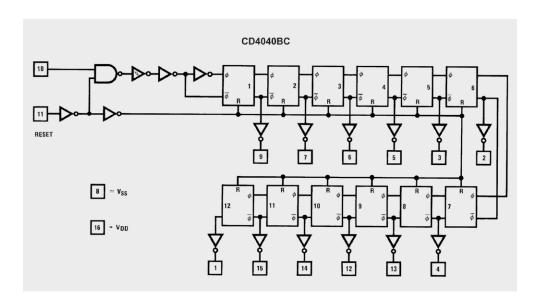

Im unteren Teil ist die "normale" Beschaltung des CD4040 und der Platinenaufdruck zu sehen. Wie der CD4040 intern aufgebaut ist, zeigt Bild 22, wobei dies natürlich nur das Blockschaltbild ist.

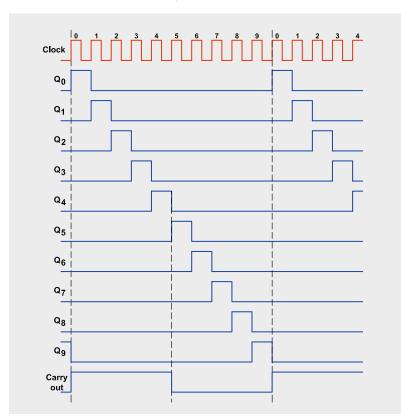

Der Zählerstand schreitet bei jedem High-Low-Übergang von Clock (Takt) um eine Stufe weiter. Die Zählerstufen bestehen aus hintereinander geschal-

Bild 21: Schaltbild des CD4040 mit Peripherie, oben: die komplette Schaltung mit Status-LEDs, unten: die Grundschaltung, rechts: der Platinenaufdruck

teten D-Flip-Flops. Der Clockausgang der folgenden Stufe ist mit dem /Q des vorigen Flip-Flops verbunden. Diese Technik bezeichnet man als Ripple-Zähler. Im Vergleich dazu liegt bei einem synchronen Zähler an allen Flip-Flops das Taktsignal an.

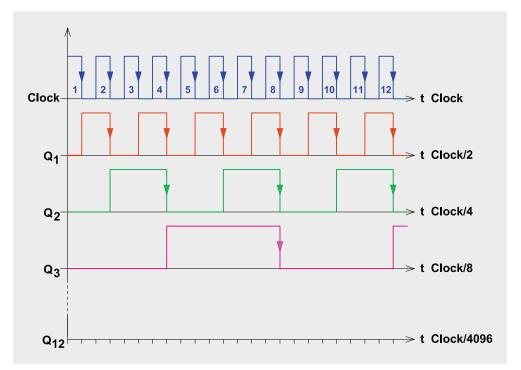

Durch jede Zählerstufe (Flip-Flop) wird die Eingangsfrequenz durch zwei geteilt. Der CD4040 besitz zwölf Zählerstufen und kann die Eingangsfrequenz damit max. durch  $2^{12} = 4096$  teilen. Wie die Ausgangssignale in Bezug auf das Clocksignal aussehen, ist im Diagramm auf Bild 23 zu sehen.

Der Reseteingang wird normalerweise auf Low gehalten und führt bei einem High einen Reset durch (siehe Tabelle auf Bild 24)

Durch eine spezielle Schaltungstechnik kann im Prinzip jeder Teilungsfaktor zwischen 2 und 4096 generiert werden. Wie dies funktioniert, ist im folgenden Abschnitt zum CD4060 erklärt.

Beim CD4040 sind nur die Zählerausgänge unterschiedlich. In Bild 24 ist die Tabelle mit den verfügbaren Zählerausgängen und den zugehörigen Teilerfaktoren zu sehen.

Wie im Abschnitt CD4060 erklärt, kann auch der CD4040 auf einen bestimmten Teilerfaktor programmiert werden.

Ein Beispiel: Wir brauchen z.B. einen Teilerfaktor von 310. In der Spalte "Zählerstandsberechnung" suchen wir uns die entsprechende Werte, um auf einen Wert von 310 zu kommen. Wir fangen mit dem größtmöglichen Teilerfaktor an, in unserem Fall 256:

$$310 - 256 = 54$$

Bild 22: Das Blockschaltbild des CD4040 zeigt das Innenleben des Schaltkreises.

Bild 23: Das Impulsdiagramm für CD4040

| Ausgang | Teilerfaktor | Zählerstand-<br>berechnung | Beispiel 1 |  |

|---------|--------------|----------------------------|------------|--|

|         |              |                            |            |  |

| Q1      | 2            | 1                          |            |  |

| Q2      | 4            | 2                          | х          |  |

| Q3      | 8            | 4                          | х          |  |

| Q4      | 16           | 8                          |            |  |

| Q5      | 32           | 16                         | Х          |  |

| Q6      | 64           | 32                         | х          |  |

| Q7      | Q7 128       |                            |            |  |

| Q8 256  |              | 128                        |            |  |

| Q9 512  |              | 256                        | х          |  |

| Q10     | 1024         | 512                        |            |  |

| Q11     | 2048         | 1024                       |            |  |

| Q12     | 4096         | 2048                       |            |  |

Es bleibt ein Rest von 54, von dem wir den nächstmöglichen Wert aus der Tabelle, also 32 abziehen. Dieser Vorgang wir so lange wiederholt, bis der Rest null ist. Wenn man sich die rechte Spalte in der Tabelle anschaut und alle Werte aus der Spalte "Zählerstandberechnung", die mit einem x gekennzeichnet sind, addiert, kommen wir auf einen Wert von 310. An den mit x markierten Ausgängen des Zählers ist demzufolge ein Jumper zu setzen.

$\bigoplus$

Summe 310

Bild 24: Ausgänge des CD4040 mit zugehörigen Teilerfaktoren und Beispiel für die Berechnung des Resets für einen Teilerfaktor 310

# © CD4017 – Dezimalzähler mit 10 Ausgängen

Bezeichnung: CD4017, HEF4017

Typ: CMOS Dezimalzähler mit 10 Ausgängen

Betriebsspannung: 3-15 V

Taktfrequenz: 2,5 MHz @ UB=5 V

12 MHz @ UB=10 V

Stromaufnahme: 0,4-0,8 mA inaktiv/ohne Last

#### **Funktion**

$\bigoplus$

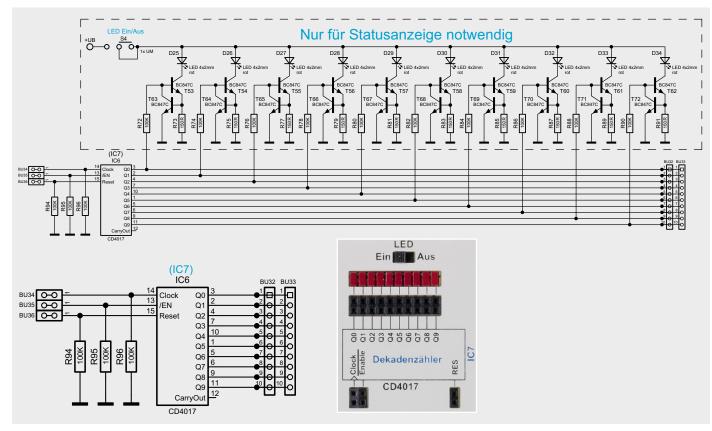

Der CD4017 ist ein synchroner Dezimalzähler mit zehn Ausgängen. Im Gegensatz zu einem Binärzähler ist immer nur einer der zehn Ausgänge aktiv, also ein 1-aus-10-Decoder. In Bild 18 ist das Schaltbild mit CD4017 und zusätzlicher Peripherie dargestellt. In Bild 19 sind die Ein- und Ausgangssignale grafisch dargestellt, um einen besseren Einblick in die Funktion zu bekommen.

Wie schon erwähnt, dient der obere Teil (Status-LED) nur zur Darstellung der Logikpegel an den Ausgängen. Mit dem Schalter S4 können die Status-LEDs abgeschaltet werden. Für die "normale" Funktion ist dieser Schaltungsteil nicht erforderlich. Im unteren Teil von Bild 18 sind der CD4017 in seiner Grundfunktion und der Platinenaufdruck zu sehen.

Bild 18: Schaltbild des CD4017 mit Peripherie, unten: CD4017 ohne Status-LEDs mit Platinenaufdruck

Bild 19: Der Signalverlauf am CD4017

| Clock | /EN | Reset | Funktion                               |

|-------|-----|-------|----------------------------------------|

|       | L   | L     | Zähler schreitet um eine Stelle weiter |

| Н     |     | L     | Zähler schreitet um eine Stelle weiter |

| Х     | Х   | Н     | Zähler wird zurückgesetzt; Q0 aktiv    |

H = High-Pegel

L = Low-Pegel

X = Zustand beliebig

Die drei Pull-down-Widerstände R94-R96 dienen dazu, die Eingänge auf einen definierten Pegel, hier auf Massepotential, zu legen. Wie bereits gesagt, müssen alle nicht benutzten Eingänge entweder auf High- oder auf Low-Pegel gehalten werden. Hierdurch wird die Verwendung dieses Bausteins vereinfacht, da die Beschaltung die Grundeinstellung darstellt. Der Reset und der /EN-Anschluss liegen somit auf Masse (Low-Pegel) und müssen nicht noch extra beschaltet werden, es sei denn, man möchte diese Funktionen nutzen. Welche Auswirkung diese beiden Steuereingänge auf die Funktion haben ist in der Tabelle (Bild 20) zu sehen. Bei einem Low-High-Wechsel am Clockeingang schreitet der Zähler um eine Stelle weiter. Da der Enable-Eingang mit dem Takteingang über ein Gatter verknüpft ist, kann dieser Pin auch zum Takten verwendet werden, wenn der Clock-Eingang auf High liegt.

Mit diesem Baustein lässt sich auf einfache Weise ein Lauflicht realisieren (Knight-Rider). Hierzu wird ein Takt mit relativ niedriger Taktfrequenz auf den Clock-Eingang gegeben. Die Ausgänge werden nun der Reihe nach eingeschaltet und man erhält ein 10-Kanal-Lauflicht. Möchte man nur ein Lauflicht mit fünf Kanälen, verbindet man den Ausgang Q5 mit dem Reseteingang. Sobald der Ausgang Q5 auf High wechselt, wird ein Reset durchgeführt und der Zähler springt zurück auf Q0. Solche Schaltungen sind im Internet zahlreich zu finden.

Bild 20: Die Wahrheitstabelle für CD4017

29.08.19 14:15

# @ CD4510 - Dezimalzähler (aufwärts/abwärts)

Bezeichnung: CD4510, HEF4510

Typ: CMOS Dezimalzähler (aufwärts/abwärts)

Betriebsspannung: 3-15 V

Frequenz: 1,5 MHz @ UB=5V

12 MHz @ UB=10 V

Stromaufnahme: 0,4 mA

### **Funktion**

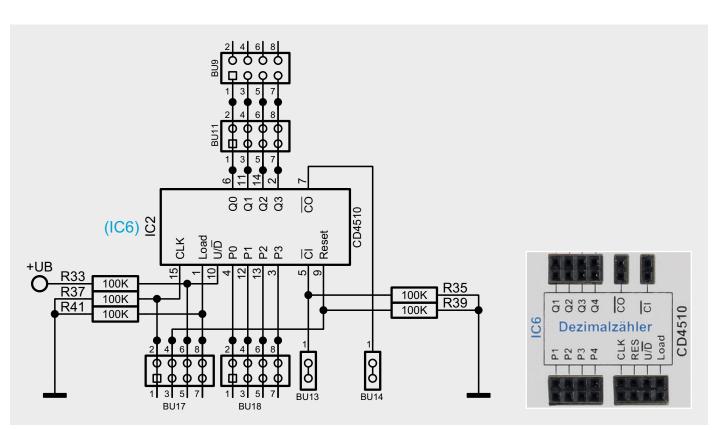

Dieser Dezimalzähler ist sowohl als Aufwärts- als auch als Abwärtszähler konfigurierbar. Zudem ist der Zähler kaskadierbar und der Zählerstand kann geladen werden. In Bild 32 ist die Schaltung mit dem CD4510 dargestellt, wobei rechts der Platinenaufdruck zu sehen ist.

Bild 32: Das Schaltbild eines CD4510 mit Platinenaufdruck

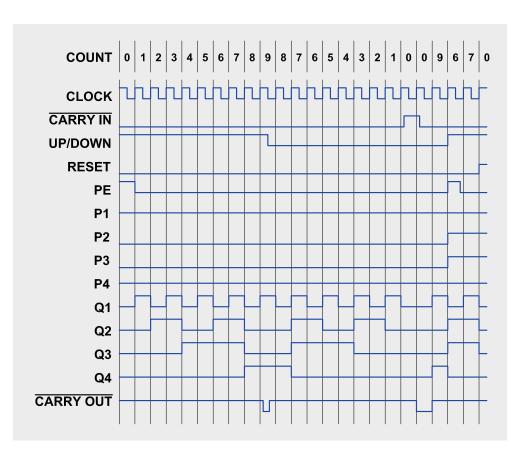

Bild 33: Die Signalverläufe des CD4510

Bei einer Low-High-Flanke am Clockeingang wird um eine Stelle weiter gezählt. Der Anschluss U/D (Up/Down) legt fest, in welche Richtung gezählt werden soll. Da der Zähler dezimal arbeitet, erfolgt nach dem Zählerstand von 9 ein Reset auf 0. Während dieses Vorgangs wird ein Carry-out-Signal erzeugt, das zur Kaskadierung für den nächsten Zähler genutzt werden kann.

Die Kaskadierung kann auf unterschiedliche Arten erfolgen. Entweder man verbindet den Carry-out (CO) mit dem Clock-Eingang der nächsten Stufe oder man legt an alle in der Kaskade befindlichen Zähler den gleichen Takt an und verbindet jeweils den Carry-out mit dem Carry-in der nächsten Stufe.

In Bild 33 sind die wesentlichen Signalverläufe dargestellt. Das parallele Laden von Daten an den Eingängen P1 bis P4 geschieht über ein High-Signal an Eingang "Load". In der Tabelle in Bild 34 sind alle Eingänge und deren Funktion noch einmal dargestellt.

| Α | В | С | D | LE | BI | Anzeige |

|---|---|---|---|----|----|---------|

| L | L | L | L | Н  | L  | 0       |

| Н | L | L | L | Н  | L  | 1       |

| L | Н | L | L | Н  | L  | 2       |

| Н | Н | L | L | Н  | L  | 3       |

| L | L | Н | L | Н  | ١  | 4       |

| Н | L | Н | L | Н  | L  | 5       |

| L | Н | Н | L | Н  | L  | 6       |

| Н | Н | Н | L | Н  | L  | 7       |

| L | L | L | Н | Н  | L  | 8       |

| Н | L | L | Н | Н  | L  | 9       |

| Х | Х | Χ | Х | Н  | Н  | Aus     |

H = High-Pegel

L = Low-Pegel

X = Zustand beliebig

Bild 35: Wahrheitstabelle für CD4543

| Clock | Reset | U/D | CI | Load |

|-------|-------|-----|----|------|

|       | L     | Н   | L  | L    |

|       | L     | L   | L  | L    |

| Х     | L     | Х   | Х  | Н    |

| Х     | Х     | Х   | Н  | Х    |

| Х     | Н     | Х   | Х  | X    |

H = High-Pegel

L = Low-Pegel

X = Zustand beliebig

Bild 34: Wahrheitstabelle für die Steuereingänge des CD4510

# © CD4543 – BCD-zu-7-Segment-Decoder (mit Speicher)

Bezeichnung: CD4543, HEF4543

Typ: CMOS BCD zu 7-Segment-Deco-

der (LCD oder LED)

Betriebsspannung: 3–15 V

Stromausgang: Max. 10 mA/Segment Stromaufnahme: 0,4 mA ohne Last

### **Funktion**

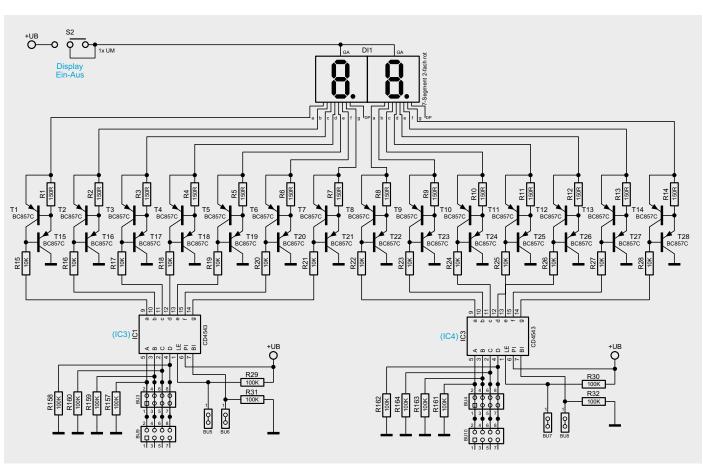

Dieser Decoder wandelt einen BCD-Code (Binary Coded Decimal) in eine 7-Segment-Ausgabe für LED-oder LC-Anzeigen um, zudem besitzt dieser Baustein noch einen Eingangsspeicher. In der Regel wird dieser Baustein für LED-7-Segmentanzeigen verwendet.

Bild 36: Schaltbild der beiden Decoder-Bausteine CD4543 mit angeschlossener 7-Segment-Anzeige

**(**

Bild 37: Vereinfachte Darstellung (ohne Strombegrenzung)

Bild 38: Platinenaufdruck der Decoder CD4543

Bild 25: Schaltbild und zugehöriger Platinenaufdruck des CD4060

Der Anschluss PI legt fest, ob eine LED-Anzeigen mit gemeinsamer Anode (PI=H) oder Katode (PI=L) verwendet werden soll. Bei LC-Displays wird an PI ein Rechtecksignal eingespeist.

Die Tabelle in Bild 35 zeigt anhand der Logikpegel, wie der Decoder funktioniert. Die Spalten A bis D sind die Eingänge, und in Spalte "Anzeige" ist der Anzeigewert zu sehen. Ein High am Anschluss BI (Blanking Input) schaltet die LED-Ausgänge ab und die Anzeige bleibt dunkel.

Für den normalen Betrieb muss der Eingang LE (Latch Enable) auf High gehalten werden. Falls Eingangsdaten nicht dauerhaft an den Eingängen A bis D anliegen, können diese im Eingangsspeicher abgelegt werden. Hierzu wird der Anschluss LE kurzzeitig auf Low gebracht, wodurch die Daten im Speicher abgelegt werden.

In Bild 36 ist die in unserem Experimentierboard verwendete Schaltung mit CD4543 und angeschlossenen LED-Anzeigen zu sehen. Die Schaltung sieht auf den ersten Blick etwas unübersichtlich aus, da für jede Segmentleitung eine Strombegrenzung integriert ist. Aus diesem Grund ist in Bild 37 eine vereinfachte Darstellung des CD4543 in der Grundschaltung zu sehen. Eine Strombegrenzung für die LED-Anzeige

ist deshalb notwendig, weil das Experimentierboard für einen weiten Spannungsbereich von 3–15 V ausgelegt ist.

Die Funktion der Strombegrenzung ist im Abschnitt "Statusanzeige" erklärt. Wenn die Anzeigeneinheit nicht benötigt wird, kann die LED-Anzeige abschaltet werden. Alle Steuereingänge sind mit Pull-up- bzw. Pull-down-Widerständen für den Betrieb mit der LED-Anzeige (gemeinsame Anode) ausgelegt. Die Daten am Eingang führen sofort zur Anzeige.

In Bild 38 ist ebenfalls auch der Platinenaufdruck für die Anzeigeneinheit zu sehen. Mechanisch sind die Decoder sehr nahe an den beiden Dezimalzählern (CD4510) positioniert. Über Jumper können die Zähler mit dem Anzeigendecoder verbunden werden, falls dies erwünscht ist. Wie dies geschieht, ist im Abschnitt "Anwendungsbeispiel 1" erklärt.

Bild 26: Blockschaltbild des CD4060

Quelle: www.st.com

$\bigoplus$

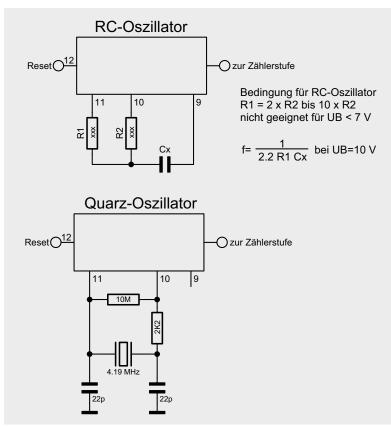

Bild 27: Beide Varianten der Oszillatorbeschaltung

# 49 CD4060 – 14-stufiger Binärzähler mit Oszillator

Bezeichnung: CD4060, HEF4060 Typ: CMOS Binärzähler

Betriebsspannung: 3–15 V

Frequenz: 0,8 MHz mit RC-Oszillator

12 MHz mit Quarzoszillator

Stromaufnahme: 0,04 µA inaktiv

2 mA aktiv

### **Funktion**

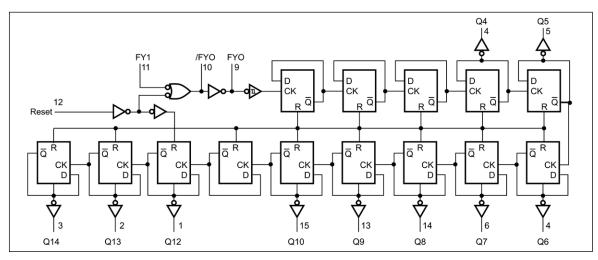

Der CD4060 ist ein Binärzähler mit 14 Stufen und einem integrierten Oszillator. In Bild 25 sind das Schaltbild des CD4060 in unserer Schaltung mit Peripherie und der zugehörige Platinenaufdruck dargestellt. Wie der CD4060 intern aufgebaut ist, zeigt das Blockschaltbild in Bild 26.

Der interne Oszillator kann als RC- oder Quarzoszillator beschaltet werden. Der Oszillator muss nicht zwingend genutzt und beschaltet werden. Pin 11 kann auch als Takteingang für extern zugeführte Signale verwendet werden. In Bild 27 sind beide Varianten für den Oszillator dargestellt. Der Hersteller empfiehlt, bei einer Betriebsspannung von weniger als 7 V keinen RC-Oszillator zu verwenden.

Der Zählerstand schreitet bei jedem High-Low-Übergang von Clock um eine Stufe weiter. Die Zäh-

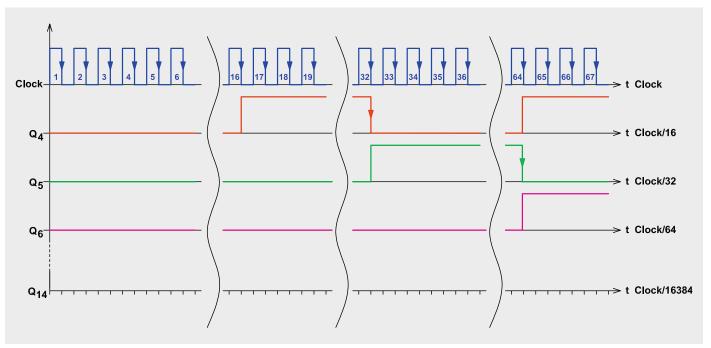

Bild 28: Signaldiagramm des CD4060

| Reset | Funktion                               |

|-------|----------------------------------------|

| н     | Alle Zählerstufen werden zurückgesetzt |

| L     | Normaler Zählerbetrieb                 |

Bild 29: Logiktabelle für den Reseteingang

lacktriangle

lerstufen bestehen aus hintereinander geschalteten D-Flip-Flops. Der Clockausgang der folgenden Stufe ist mit dem /Q des vorigen Flip-Flops verbunden. Diese Technik bezeichnet man als Ripple-Zähler. Im Vergleich dazu liegt bei einem synchronen Zähler an allen Flip-Flops das Taktsignal an.

Durch jede Zählerstufe (Flip-Flop) wird die Eingangsfrequenz durch zwei geteilt. Der CD4060 besitzt 14 Zählerstufen und kann die Eingangsfrequenz damit max. durch 2<sup>14</sup> = 16.384 teilen. Hierbei ist zu beachten, dass die Ausgangssignale der ersten drei Flip-Flops und der Ausgang Q11 nicht nach außen geführt sind. Wie die Ausgangssignale in Bezug auf das Clocksignal aussehen, ist im Diagramm Bild 28 zu sehen.

Dieser Zähler wird gerne als Basisgenerator verwendet, da er einen Oszillator integriert hat. In unserer Schaltung wird standardmäßig als Quarz eines mit einer Frequenz von 4,194304 MHz verwendet. An Q14 liegt somit eine Frequenz von 256 Hz an.

Der Reseteingang wird normalerweise auf Low gehalten und führt bei einem High einen Reset durch (siehe Tabelle auf Bild 29).

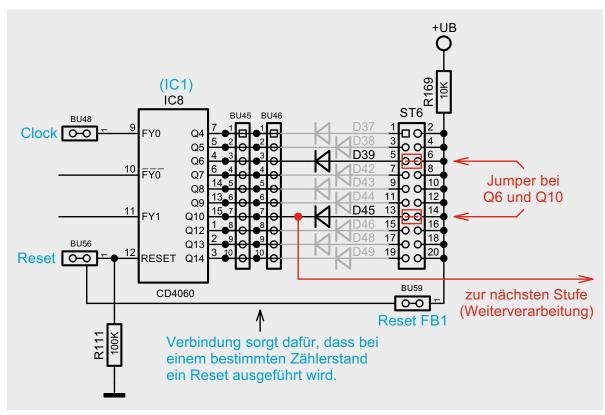

Durch eine spezielle Schaltungstechnik kann im Prinzip jeder Teilungsfaktor zwischen 16 und 16.384 generiert werden. Hierzu muss bei einem bestimmten selbst gewählten Zählerstand ein Reset durchgeführt werden. Die Schaltungstechnik hierfür ist auf dem Experimentierboard schon vorhanden. Über zuschaltbare Dioden kann mittels Steckbrücken (Jumper) ein bestimmter Zählerstand ausgewählt werden, der zu einem Reset führt. Schauen wir uns das Beispiel in Bild 30 an. Die dargestellte Rückkopplung mit Dioden nennt man Wired-And, zu Deutsch: eine verdrahtete Und-Logik. Voraussetzung für einen Reset durch diese Logik ist eine Verbindung mit dem Anschluss Reset FB1 und dem Reset vom CD4060. Dazu ist auch der Hinweis zur Rückkopplung im Anwendungsbeispiel 1 zu beachten.

### **Funktionsbeispiele**

Bei einem Zählerstand von 0 befinden sich alle Zählerausgänge (Q4 bis Q14) auf Low. Über die Dioden wird der Anschluss "Reset FB1" auf Low-Pegel gehalten, obwohl ja über den Pull-up-Widerstand R169 ein High-Signal anliegt. Erst wenn der Ausgang Q6 und Q10, die ja über Dioden mit dem Reset (FB1) verbunden sind, gleichzeitig High-Pegel führen, geht der Anschluss "Reset FB1" auf High und führt einen Reset beim CD4060 durch. Schauen wir uns nun an, bei welchem Zählerstand hier ein Reset durchgeführt wird.

Der Ausgang Q6 teilt ja das Clocksignal durch (26), was einen Faktor von 64 ergibt. Beim Ausgang Q10 ergibt sich ein Teilungsfaktor von 210 = 1024. Leider kann man die Zählerstände so nicht addieren, sondern muss diese durch zwei dividieren. Der Grund ist, dass z. B. der Zählerstand 1024 von Q10 erst bei der vollen Periode erreicht wird. Auf der Hälfte dieser Zeit, also bei 512, wechselt der Q9-Ausgang aber schon auf High-Pegel. Um die Rechnerei zu vereinfachen, ist in der Tabelle (Bild 31) noch eine zweite Spalte eingefügt, die zur Berechnung des Zählerstandes für den Reset dient.

Jetzt zählt man die Teilerfaktoren, also 64 und 1024 zusammen und erhält den Zählerstand (1088), bei dem ein Reset durchgeführt wird. Jetzt kommt die Mathematik wieder ins Spiel. Nach 1088 Takten wird demnach ein Reset durchgeführt. Bei einer Oszillatorfrequenz von 4,194304 MHz ergibt sich ein Taktzyklus von 238 ns. Multipliziert man diesen Wert mit dem errechnete Zählerstand von 1088, ergibt sich eine Zeit von 1088 x 238,4 ns = 259 µs, was einer Frequenz von 3855 Hz entspricht. Man kann auch Oszillatorfrequenz/Zählerstand rechnen:

Frequenz/Zählerstand = 4,194304 MHz/1088 = 3,855 kHz

Möchte man eine bestimmte Frequenz aus der Oszillatorfrequenz ableiten, sind der entsprechende Tei-

lungsfaktor und der Zählerstand zu ermitteln. Da die Zählerausgänge Q1 bis Q3 nicht zugänglich sind, können nicht alle Teilerfaktoren verwendet werden. In der Tabelle in Bild 31 sind die Teilerfaktoren für die Ausgänge des CD4060 dargestellt. Hier ist auch ein zweites Beispiel zu sehen. Um den Lerneffekt zu vergrößern, haben wir das Ergebnis unten nicht eingetragen. Hier sollte man selber die Ausgangsfrequenz berechnen. Nur so lässt sich der Berechnungsweg erlernen. Leider können wir in diesem Artikel nicht die gesamte Digitaltechnik erklären. Hier heißt der Lernprozess "learning by doing".

Für die Weiterverarbeitung des gewonnenen Signals, z. B. als Taktsignal für eine weitere Zählerstufe, sollte man auf keinen Fall das Resetsignal verwenden. Das Resetsignal ist zeitlich gesehen sehr kurz (Spike) und entspricht der Verzögerungszeit eines CMOS-Gatters, bis tatsächlich ein Reset ausgeführt wird. Dies sind nur wenige Nanosekunden, deshalb sollte man immer den hochwertigsten Zählerausgang, in unserem Fall für Beispiel 1 ist das der Q10-Ausgang, verwenden (siehe Bild 30).

ELV

Bild 30: Mit dieser Beschaltung wird bei Zählerstand 1088 ein Reset durchgeführt.

| Ausgang | Teilerfaktor | Zählerstand- berechnung Beispiel 1 |   | Beispiel 2 |

|---------|--------------|------------------------------------|---|------------|

|         |              |                                    |   |            |

| Q1      | 2            | nicht herausgeführt!               |   |            |

| Q2      | 4            | nicht herausgeführt!               |   |            |

| Q3      | 8            | nicht herausgeführt!               |   |            |

| Q4      | 16           | 8                                  |   | х          |

| Q5      | 32           | 16                                 |   |            |

| Q6      | 64           | 32                                 | х |            |

| Q7      | 128          | 64                                 |   |            |

| Q8      | 256          | 128                                |   | х          |

| Q9      | 512          | 256                                |   |            |

| Q10     | 1024         | 512                                | х |            |

| Q11     | 2048         | nicht herausgeführt!               |   |            |

| Q12     | 4096         | 2048                               |   | х          |

| Q13     | 8192         | 4096                               |   |            |

| Q14     | 16384        | 8192                               |   | х          |

Summe

Bild 31: Diese Tabelle zeigt, welche Ausgänge am CD4060 zur Verfügung stehen und wie der Zählerstand für einen Reset berechnet wird.

ELVjournal 5/2019

???

544