# Digitale Ein-/Ausgabebaugruppe für die ELV-DSP50-Karte Teil 6

Für die ELV-DSP50-Karte entwickelt, verfügt diese Zusatzbaugruppe über 8 digitale Ausgänge mit jeweils 250 mA Strombelastbarkeit, 8 opto-isolierte Eingänge sowie die Anschlußmöglichkeit von 4 Sendern und 4 Empfängern für Kunststoff-Lichtwellenleiter.

## **Allgemeines**

Die einfachste zu realisierende Anwendung für den DSP ist die schnelle Verarbeitung digitaler Signale. Zu diesem Bereich gehören unter anderem die Wegmessung über incrementale Geber oder eine Drehzahlmessung, welche aufgrund der Prozessorleistung auf mehreren Kanälen gleichzeitig erfolgen kann.

Um diese Aufgabe zu lösen, haben wir für das DSP-Board eine digitale Ein-/Ausgabekarte entworfen, die über 8 digitale Ausgänge mit jeweils 250 mA Belastbarkeit, 8 opto-isolierte Eingänge sowie optional 4 Sender und 4 Empfänger für Kunststoff-Lichtwellenleiter verfügt.

Anhand dieser Erweiterungskarte wollen wir auch die ersten Beispiele zur Programmierung des DSP vorstellen. In diesem Artikel werden dafür nur die hardwarebezogenen Teile dargestellt, während das Gesamtprogramm über alle E/A-Funktionen in einem Datenloggerprogramm zusammengefaßt wird, auf der DSP-Tool-Disk enthalten ist.

## Die Schaltung der E/A-Karte

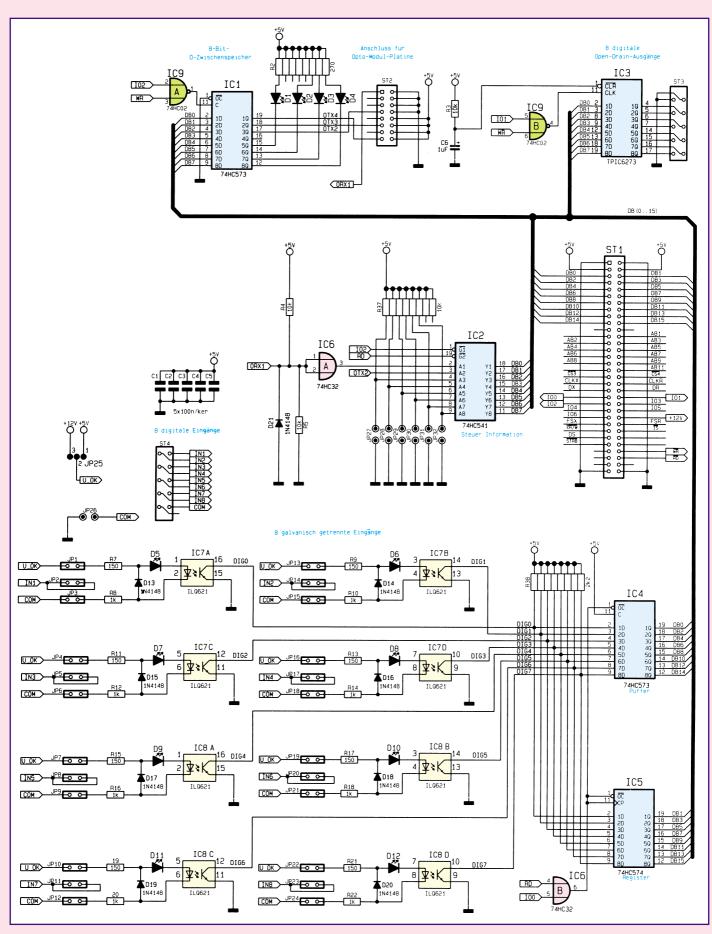

Die in Abbildung 1 dargestellt E/A-Karte wird über den DSP-Bus-Anschluß (Extender) mit dem DSP-Prozessor verbunden. Benötigt werden von den Signalen des 64poligen Anschlusses der Datenbus, die

I/O-Select-Signale und die Lese-/Schreibleitung.

Die digitalen Ein- und Ausgänge werden über zwei Flachbandleitungen von dieser Karte mit den beiden 9poligen Sub-D-Buchsen der DSP50-Karte verbunden. Der Anschluß der Kunststoff-Lichtwellenleiter (4 Sender, 4 Empfänger) erfolgt über eine zusätzliche kleine Leiterplatte, die an einem PC-Slotblech befestigt ist. Die Verbindung der kleinen Platine am Slotblech mit der E/A-Karte erfolgt ebenfalls über ein Flachbandkabel.

## Die digitale Ausgabe

Bei der digitalen Ausgabe haben wir uns für einen Ausgang mit mittlerer Leistung entschieden, so daß z. B. kleine Schrittmotoren direkt steuerbar sind. Gesteuert wird der 8fach-Open-Drain-Ausgang der E/A-Karte durch eine Datenausgabe auf dem Port 1 des DSP, wobei die unteren 8 Bit in den Puffer geladen werden.

Die 8 zur Verfügung stehenden Open-Drain-Ausgänge sind jeweils mit 250 mA belastbar, wobei Spannungen bis zu 36 V zulässig sind.

Diese Ausgänge können somit direkt für die Ansteuerung von Relais, Anzeigen oder ähnlichem dienen. Bei voller Stromauslastung ist eine entsprechende Dimensionierung der Anschlußleitung zu beachten

Zur Ansteuerung einer nachgeschalteten Logik sind die Ausgänge mit PullupWiderständen zu beschalten. Da die Flankensteilheit der Treiberausgänge im Bereich bis zu 1 µs liegt, sind Schmitt-Trigger-Eingänge bei der nachfolgenden Logik sinnvoll.

Wie bereits erwähnt, erfolgt die Datenausgabe an Port 1 des DSP.

## Die digitale Eingabe

Die digitale Dateneingabe erfolgt galvanisch getrennt über Optokoppler, ebenfalls mit 8 Bit Breite.

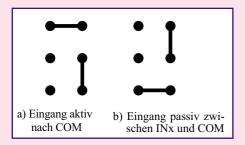

Über Kodierbrücken (Jumper) können die Eingänge im passiven oder aktiven Mode arbeiten (Abbildung 2).

Betrachten wir zunächst den passiven Mode, d. h. die Leuchtdioden der Eingangs-Optokoppler werden direkt mit einem Strom beaufschlagt, der zwischen 5 und 10 mA liegen sollte. Dazu sind die Kodierbrücken der identisch aufgebauten Eingangskanäle entsprechend Abbildung 2 a zu stecken. Die Werte der Eingangswiderstände richten sich nach der Betriebsspannung des Steuersignals. Bei 5 V Eingangssignal ist als Gesamtwiderstand für jeden Kanal mit etwa 150  $\Omega$  einzusetzen.

Öffnet man den Kodierstecker JP 26 (von COM nach GND), so sind die Eingänge von der DSP-Karte und somit auch vom PC völlig isoliert. Im aktiven Mode werden die Kodierstecker entsprechend Abbildung 1 b gesteckt, wobei keine galvanische Trennung zwischen der DSP-Karte und den 8 Eingängen besteht.

Bild 1: Hauptschaltbild der digitalen E/A-Karte

Bild 2: Betriebsmode der Optokoppler-Eingänge

Zur Versorgung der Eingangsschaltungen ist mit JP 25 +5V oder +12V auszuwählen. Der Strom fließt durch die Leuchtdioden, wenn der entsprechende Eingang (IN 1 bis IN 8) nach Masse gezogen wird. In diesem Betriebsmode ist die Kodierbrücke JP 26 unbedingt zu stecken.

Die Ausgänge der Optokoppler IC 7, IC 8 werden parallel auf ein Register (IC 5) und einen Puffer (IC 4) geführt. Während die Daten über den Puffer direkt zum Rechner gelangen und hier die geraden Bitpositionen belegen, übernimmt das Register die Daten mit der steigenden Flanke des Lesesignales, also am Ende des Lesevorganges.

Die damit auf den ungeraden Bitpositionen hinterlegten Daten stellen beim Lesen der Digitaleingänge die Belegung der vorhergehenden Abfrage dar, was für den Incremental-Algorithmus günstig zu verwenden ist.

Die Eingabe in den DSP erfolgt sortiert mit 16 Bit Breite auf den Port 0 des DSP.

# Die Ein-/Ausgänge über Lichtwelen-Leiter und die Steuerbits

Für die weitere Kommunikation mit der

Außenwelt besteht die Möglichkeit, Kunststoff-Lichtwellenleiter einzusetzen.

Dazu sind an der Leiterplatte 4 LWL-Sender und 4 LWL-Empfänger anschließbar. Die Sende- und Empfangsmodule befinden sich auf einer abgesetzten Leiterplatte, die an einem Slotblech befestigt wird.

Mit der Opto-Schnittstelle ist die Realisierung eines 3-Draht-Interface für Einund Ausgabe oder ein bidirektionaler Betrieb über 4 Leitungen möglich. Im weiteren Verlauf dieser Artikelserie wird das Opto-Interface noch im Zusammenhang mit einem abgesetzten AD-Wandler zur potentialfreien Messung von Spannungen eingesetzt.

Die Leiterplatte wurde für universelle Einsatzzwecke an der DSP50-Karte konzipiert. Je nach Einsatz ist daher nicht die vollständige Bestückung der Platine erforderlich.

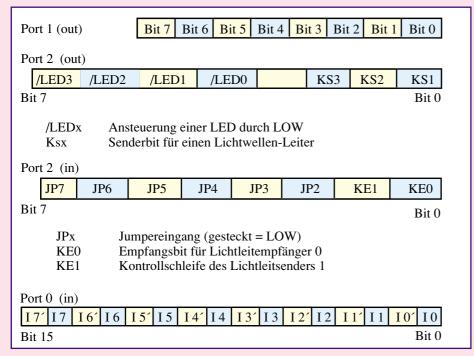

6 Kodierstecker (Jumper) am Bus-Leistungstreiber IC 2 dienen zur Einstellung von Steuerinformationen. Des weiteren sind am Ausgang des 8Bit-D-Zwischenspeichers IC 1 4 LEDs zur Statusanzeige vorhanden, die zusammen mit den Lichtwellenleiter-Modulen einen Port belegen. Der hierfür verwendete Port 2 hat damit die in Abbildung 3 dargestellte Gesamtbelegung.

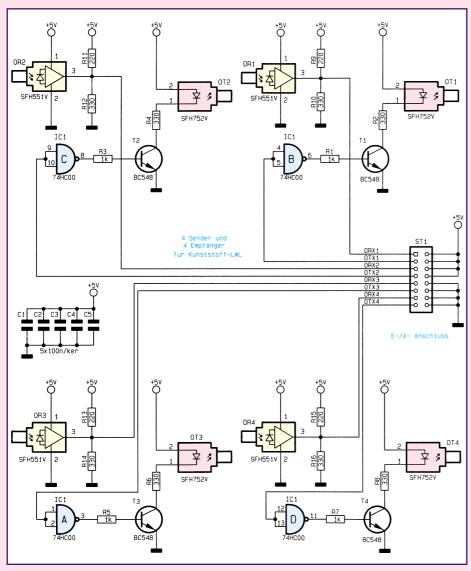

#### **Die Opto-Modul-Platine**

Wie schon erwähnt, befinden sich die Sender und Empfänger für den Anschluß der Kunststoff-Lichtwellenleiter auf einer eigenen abgesetzten Platine. Die Verwendung der Kunststoff-LWL, dessen Schaltung in Abbildung 4 zu sehen ist, hat besonders im Hinblick auf die elektromagnetische Verträglichkeit große Vorteile, da keine elektrischen Signale außerhalb des PCs gelangen. Das ausschließlich innerhalb des PCs zu verlegende Flachbandkabel führt nur geringe Signalströme und ist durch seine Anschlußbelegung (zwischen jeder Signalleitung liegt eine Masseleitung) gut geschirmt.

Auf der kleinen Modul-Platine sind neben den 4 optischen Sendern OT 1 bis OT 4 und den 4 optischen Empfängern (OR 1 bis OR 4) noch ein 4fach UND-Gatter, 4 Transistoren, 5 Kondensatoren und wenige passive Widerstände (R 1 bis R 16) vorhanden.

Das für eine spätere Baugruppe benötigte schnelle serielle Interface auf Lichtwellen-Leiter-Basis dient z. B. zur Ansteuerung eines abgesetzten Analog-Digital-Umsetzers. Für diese Anwendung sind dann 3 optische Sender und 1 optischer Empfänger zu bestücken.

## Einsatz zur Auswertung von incrementalen Gebern

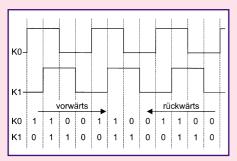

Die digitale Wegmessung erfolgt heute allgemein mittels incrementaler Geber. Diese erzeugen bei einer Bewegung zwei phasenversetzte Rechtecksignale, wodurch man außer dem zurückgelegten Weg auch die Bewegungsrichtung bestimmen kann. Im Gegensatz zur Hardwareauswertung dieser Signalfolgen hat man bei der Softwareversion die Möglichkeit, unterschiedliche Algorithmen einzusetzen. Um eine Lösung zu erarbeiten, ist in Bild 5 der Signalverlauf eines Gebers dargestellt.

Die einfachste Form der Auswertung stellt die Abfrage der digitalen Eingänge auf Veränderung und die anschließende Auswertung der veränderten Flanke dar. Da diese Methode ein relativ langes und damit langsames Programm ergibt "wollen wir uns mit der Impulsauswertung über eine Tabelle befassen.

In der Hardware hatten wir vorbereitend für diese Anwendung bereits die erforderlichen Bits mit der "Belegung der vorhergehenden Abfrage" vorgesehen. Diese ersparen uns sehr viel Programm, da die Umspeicherung des aktuellen Wertes auf den alten Wert und die Überlagerung von altem und neuem Wert entfällt. Wir haben die sich ergebenden Kombinationen in Tabelle 1 dargestellt.

In den Tabellen sind die Ausgangsbelegungen für ein Doppelscanning eingetragen, was bedeutet, daß je Impulsperiode zwei Zählschritte generiert werden. Setzt man in jeder Tabelle den unteren Ausgabewert auf 0, so entsteht ein Einfachscanning. Man erhält vier Zählschritte je Periode, wenn alle Werte einer Tabelle auf jeweils den gleichen Wert gesetzt werden. Durch eine einfache Manipulation der Ta-

Bild 3: Portbelegung des DSP

Bild 4: Schaltbild der Opto-Modul-Platine

belle läßt sich also die Auflösung ändern.

Alle acht hier nicht vorkommenden Belegungen entstehen durch Fehlschaltungen (z. B. Kontaktprellen), im Fall einer Richtungsumkehr oder wenn keine Veränderung eingetreten ist. Sie ergeben keine Reaktion und damit den Ausgabewert 0.

Die Umsetzung in ein Programm ist damit sehr einfach: Mit den anliegenden Daten einer Signalgruppe von 4 Bit wird

Bild 5: Impulsfolge bei incrementalen Gebern

eine Tabelle adressiert und deren Inhalt zum Zähler addiert. Es ergibt sich damit ein recht einfaches Programm zur Auswertung (Tabelle 2).

Betrachtet man die Ausführungszeit, so benötigt man für die Auswertung einschließlich Aufruf etwa 50 Takte. Schreibt man die Ergebnisse in ein byteweises Dualport-RAM, so werden für die Datenübertragung weitere 70 Takte benötigt. Ein Auswertezyklus dauert damit 3  $\mu$ s. Um sicher zu sein, daß alle Änderungen der Eingänge erfaßt werden, ist es empfehlenswert, die Periode des Eingangssignales mindestens 8mal abzutasten. Das ergibt dann eine minimale Periodendauer am Eingang von 24  $\mu$ s. Beim Doppelscanning in unserem Beispiel sind das etwa 83000 Zählschritte je Sekunde und Kanal.

Da das Ergebnis aber nicht mit einer Aktualisierungsgeschwindigkeit von 333333 Datensätzen/s benötigt wird, kann man durch eine Verteilung und Reduzierung der Datenübertragung die effektive Abtastrate noch erhöhen.

Zum Test des Programms sind die Eingänge paarweise mit Tastenschaltern zu beschalten. Durch Betätigen der Tasten in unterschiedlicher Reihenfolge läßt sich der Zählvorgang erreichen. Für Testzwecke ist auch die Mechanik einer ausgedienten Maus geeignet, deren Lichtschrankensignale über Gatter zur Ansteuerung dienen. Es ergibt sich damit eine Bewegungsanzeige in zwei Achsen.

## Einsatz zur Drehzahlmessung

Die Bestimmung einer Drehzahl aus den Eingangsimpulsen gestaltet sich etwas einfacher. Eigentlich müßten wir dazu eine Frequenzmessung durchführen, das heißt die Impulse je Sekunde zählen. Da der DSP aber über keinen Zählereingang verfügt, lösen wir das Problem über eine Zeitmessung. Dazu initialisieren wir den internen Timer - im Programmbeispiel auf 20µs-Interrupts - und incrementieren bei jedem Interrupt ein Zählregister für jeden Meßkanal. Das Hauptprogramm überprüft die Eingangsleitungen auf einen 0-1-Flankenwechsel, was sich durch das mit anliegende "alte" Bit sehr einfach gestaltet. Ist ein Flankenwechsel aufgetreten, so wird der Zählerwert abgelegt und der Zähler zurückgestellt.

Das Ergebnisregister enthält damit die Periodendauer des Eingangssignales mit P=Registerinhalt \* 20µs. Unter Berücksichtung der Impulse (Signalperioden) des Sensors je Umdrehung kann das Ergebnis in Umdrehungen/Minute umgerechnet werden. Der Arbeitsbereich der Drehzahlmessung läßt sich durch eine Änderung des Timerwertes beeinflussen. Sollte ein größerer Arbeitsbereich erforderlich sein, so müssen die Zählregister auf 32 Bit Datenbreite umgestellt werden, so wie es im Incremental-Programm erfolgte.

Tabelle 1: Kombination eines incrementalen Gebers

Vorwärtsbewegung

| K3** | K2* | K1** | K0* | Kodierung | Ausgabe |

|------|-----|------|-----|-----------|---------|

| 0    | 0   | 0    | 1   | 01h       | 0       |

| 0    | 1   | 1    | 1   | 07h       | +1      |

| 1    | 1   | 1    | 0   | 0eh       | 0       |

| 1    | 0   | 0    | 0   | 08h       | +1      |

Rückwärtsbewegung

| K3** | K2* | K1** | K0* | Kodierung | Ausgabe |  |  |  |

|------|-----|------|-----|-----------|---------|--|--|--|

| 0    | 0   | 1    | 0   | 02h       | 0       |  |  |  |

| 0    | 1   | 0    | 0   | 04h       | -1      |  |  |  |

| 1    | 1   | 0    | 1   | 0ch       | 0       |  |  |  |

| 1    | 0   | 1    | 1   | 0bh       | -1      |  |  |  |

<sup>\*</sup> direkter Eingang

<sup>\*\*</sup> verzögerter Eingang

#### Tabelle 2: Programm zur Auswertung von Incrementalgebern

```

; Programm zur Auswertung von 4 Incrementalgebern

.ds

Datensegment

tmp3

.ber

Eingabepuffer

incK0l

low (+0)

.ber

Incremental-Kanal 0

incK0h

.ber

high(+1)

: Incremental-Kanal 1

incK11

.ber

1

incK1h

.ber

endinc

.ber

inclen

.const endinc-incK0l

Arbeitstabelle 2-fach-Scantabelle

word

.word

0

;0001

.word

0

;0010

.word

0

;0011

;0100

.word

.word

:0101

.word

0

; 0 1 1 0

; 0 1 1 1

.word

+1

;1000

.word

+1

; 1 0 0 1

; 1 0 1 0

.word

.word

0

.word

; 1011

; 1 1 0 0

; 1 1 0 1

.word

.word

; 1110

.word

.word

:1111

Auswertung eines Incrementalgebersatzes

Takte

; einlesen Digitalkanäle2

increm: in

tmp3,0

larp

ar3

1

; 1. Sensor-Satz

lacl

tmp3

: holen Daten

1

#0fh

and

; add basisadr. der Tabelle

add

#tabelle

2

samm dar3

Ablage in AR3

incK0h,16

lacc

lade ACH

or

incK0l

lade ACL

add

Wert aus Tabelle

sacl

incK0l

Ergebnis ablegen

sach incK0h

; 2. Sensor-Satz

lacl tmp3

: holen Daten

bsar

; 4 Bit rechts = 2.Paar

#0fh

... 9

and

weiter wie 1. Sensor-Satz

; 3. Sensor-Satz

... 11

lacl tmp3

bsar #8

; 4. Sensor-Satz

... 11

lacl

tmp3

#12

bsar

1

ret

Summe = 47 Takte

Initialisieren der Zählregister (:= 0)

initinc:

lacc

#0

larp

ar1

ar1.#incK0l

lar

#endinc-incK0l

rpt

; Löschen RAM-Bereich

sacl

ret

```

Im "ELVjournal 3/97" stellen wir den Nachbau und die Inbetriebnahme mit einem Testprogramm vor, gefolgt von einem an die E-/A-Baugruppe anschließbaren, abgesetzten AD-Wandler mit Lichtwellenleiter-Anschluß.

Tabelle 3: Auswertung der Digitaleingänge für eine 3-Kanal-Periodendauermessung

```

Ansteuerung der INPUT-Karte

Auswertung der Digitaleingänge (3 Kanal Periodendauermessung)

: Datensegment

.ber

tmp2

: Eingangswert

; Ausgabewerte

perK0 .be

: Periodendauer 0

.ber

perK1

.ber

Periodendauer

.ber

; Periodendauer 2

Zählregister

cnt0

.ber

Zähler 0

; Zähler 1

; Zähler 2

cnt1

.ber

cnt2

.ber

endper

.ber

perlen

.const

endper-perK0

Auswertung der Zeitddauermessungen

pergeber:

tmp2.0

; lesen Digitaleingänge

in

; Kanal 0 ( = Eingangsleitung 0 )

tmp2

#03h

lacc

: Bit 0.1

and

bend pgeber1,neq; keine 0-1-Flanke da; Änderung Kanal 0

lacc

cnt0

Zähler lesen

perK0

#0,cnt0

sacl

Zähler in Ausgaberegister

; Zähler löschen

splk

pgeber1:

lacc

tmp2

#0ch

: Bit 2.3

and

#4

Test auf 0-1-Flanke

sub

bend pgeber2,neq; keine; Anderung Kanal 1

lacc

cnt1

sacl

perK1

#0,cnt1

splk

pgeber2:

tmp2

#30h

lacc

; Bit 4,5

and

#10h

Test auf 0-1-Flanke

sub

bend pgeber3,neq; keine; Änderung Kanal 2

lacc

cnt2

perK2

#0,cnt2

sacl

splk

pgeber3:

Init für Periodendauer-Messung

initper: ldp

h1

; Datensegment

zap

larp

ar1,#perK0

lar

#endper-perK0

rpt

; Löschen RAM-Bereich

sacl

kein Interrupt

Zero-Page

Timer-Reg. =200 =>10MHz/200 =50KHz=20µs

Timer_Int enable

#0

ldp

#199,prd

splk

#8,imr

opl

splk

#20h,tcr

Start Timer

splk

ldp

clear + pending Int

Datensegment

#8,ifr

b1

; Interrupt erlauben

ret

Interrupt-Routine für Timer

(AC und Status wird automatisch gerettet)

timer:

lacc

cnt0

add

#Offffh

and

; Überlauf => nicht speichern

bend

tim1,eq

sacl

cnt0

tim1:lacc

cnt1

add

#Offffh

and

; Überlauf Zähler

bend

tim2,eq

sacl

cnt1

tim2:lacc

cnt2

add

#Offffh

and

; Überlauf Zähler

bend

tim3,eq

cnt2

sacl

tim3:rete

```